## ECE321 – Electronics I

Lecture 11: CMOS Inverter: VTC & ITC

### Payman Zarkesh-Ha

Office: ECE Bldg. 230B

Office hours: Tuesday 2:00-3:00PM or by appointment

E-mail: <u>pzarkesh.unm.edu</u>

## Review of Last Lecture

- **□** BASIC CMOS Inverter

- Resistive load inverter

- □ Introduction to SPICE

## Today's Lecture

- □ CMOS Inverter

- □ Voltage Transfer Characteristics (VTC)

- Switching threshold voltage

- Output high voltage

- Output low voltage

- Input high voltage

- Input low voltage

- □ Current Transfer Characteristics (ITC)

- Peak current

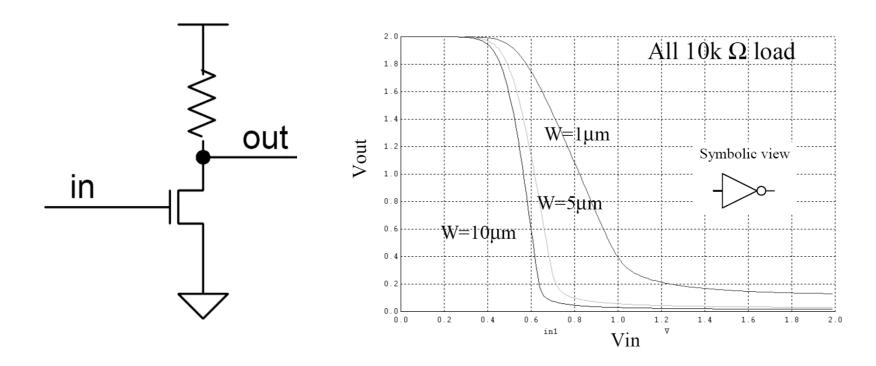

#### Review: Resistive Load Inverter

- □ A resistive load inverter consists of a pull down NMOS and a pull up resistor

- When the output is high, there is no current drawn from VDD

- When the output is high, a DC current is drawn from VDD

### Pseudo NMOS Inverter

- ☐ Since a resistor is so big, it's better to use a single PMOS transistor that is always on:

- PMOS pull up

- NMOS pull down

- ☐ Why don't we use NMOS pull up?

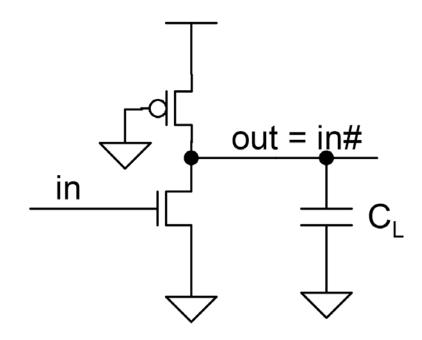

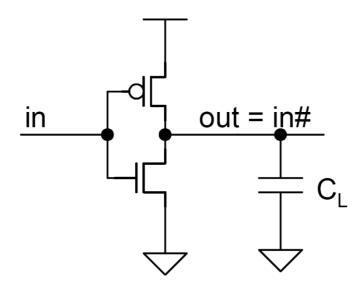

#### **CMOS Inverter**

- □ CMOS inverter is comprised of

- PMOS pull up

- NMOS pull down

- □ Advantages

- No direct path from V<sub>DD</sub> to GND (zero static power except for leakage)

- Better noise margin (Rail-to-rail output swing)

- Ratio-less logic (output level not depend on gate size)

- Always finite resistance to V<sub>DD</sub> or GND

- Very high input impedance

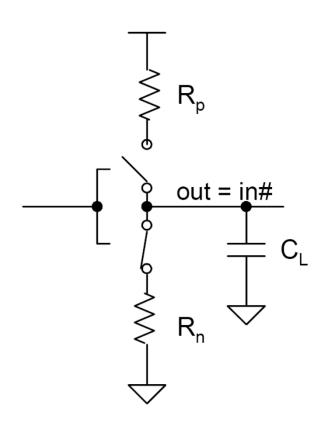

## Switching model of CMOS Inverter

- □ Treat each transistor as either on or off

- □ Each transistor has an on resistance

- This isn't a bad model as long as the input transition is quite a bit faster than the output transition and it's very intuitive

- □ Delay of the gate depends of the effective transistor resistant and load capacitance

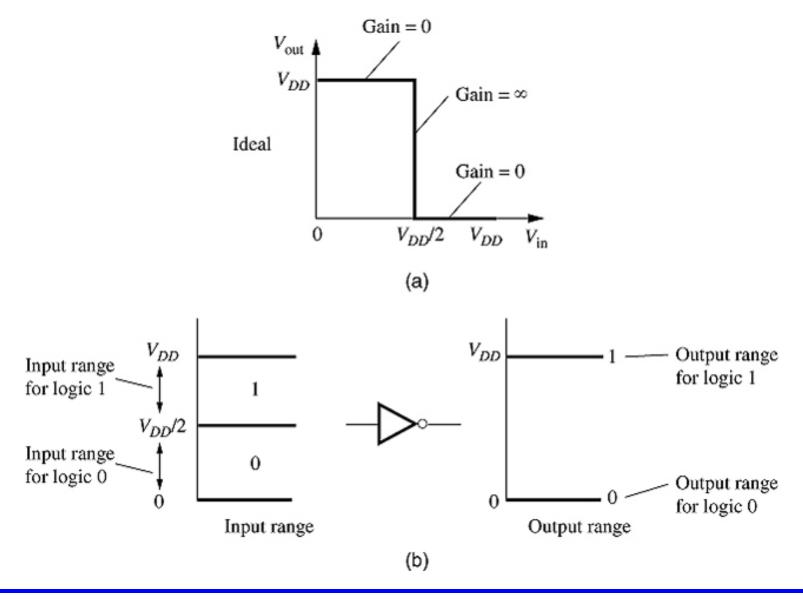

## Ideal Voltage Transfer Characteristic VTC

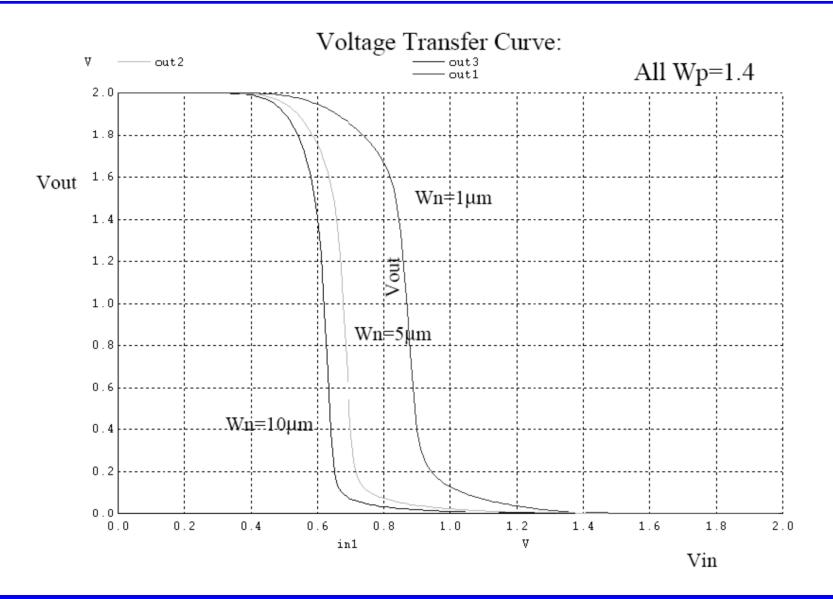

## **CMOS Inverter VTC**

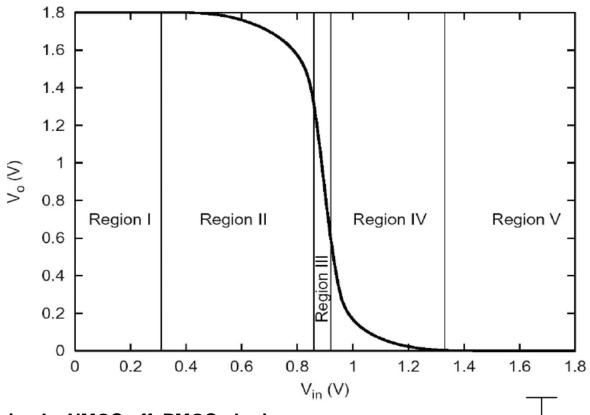

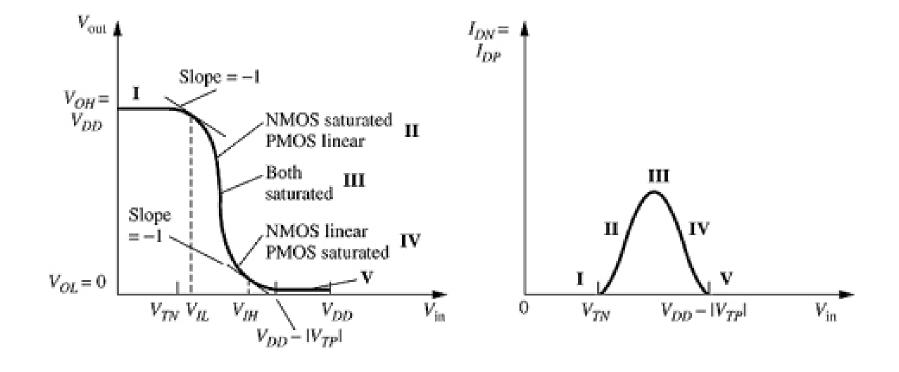

### Closer Look at CMOS Inverter VTC

- ☐ Region I NMOS off, PMOS ohmic

- ☐ Region II NMOS saturated, PMOS ohmic

- □ Region III NMOS saturated, PMOS saturated

- ☐ Region IV NMOS ohmic, PMOS saturated

- □ Region V NMOS ohmic, PMOS off

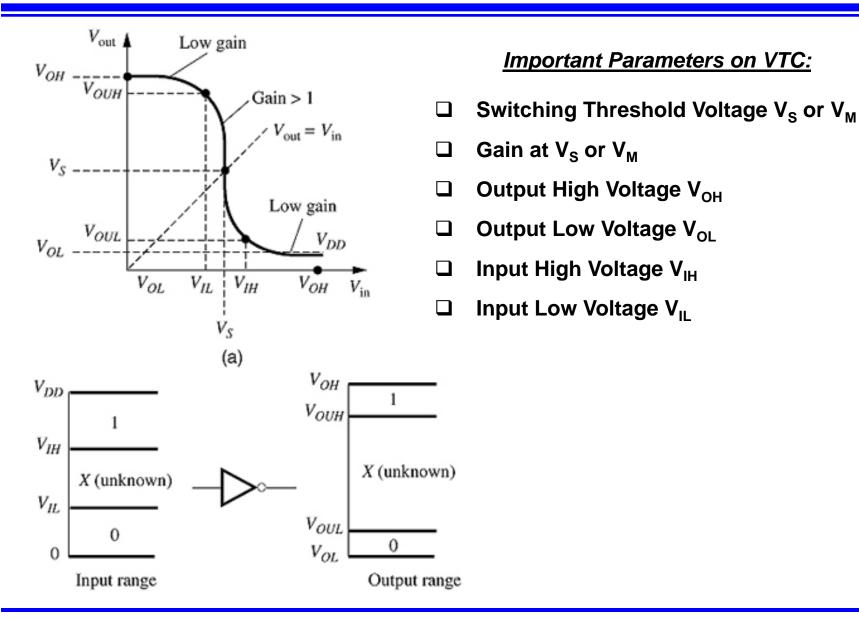

### VTC Characterization

Slide: 11

## CMOS Inverter Switching Threshold

- $\square$  How to compute  $V_M$  in CMOS logic gate?

- Use current equation in saturation to compute V<sub>M</sub>

- Assume long channel model, we will get:

$$V_{M} = \frac{\sqrt{\frac{K'_{p}(W/L)_{p}}{K'_{n}(W/L)_{n}}} \left(V_{DD} - \left|V_{Tp}\right|\right) + V_{Tn}}{1 + \sqrt{\frac{K'_{p}(W/L)_{p}}{K'_{n}(W/L)_{n}}}}$$

• To set  $V_M = V_{DD}/2$  for a symmetric CMOS inverter, we need to have:

$$\frac{\mathbf{W}_{p}}{\mathbf{W}_{n}} = \frac{\mu_{n}}{\mu_{p}} \left[ \frac{\mathbf{V}_{DD} - 2\mathbf{V}_{Tn}}{\mathbf{V}_{DD} - 2|\mathbf{V}_{Tp}|} \right]^{2}$$

## Example: Switching Threshold Voltage

Compute the ratio of nMOS and pMOS transistor width to obtain a symmetric inverter for a 0.18  $\mu$ m technology in which  $\mu_n = 360 \text{ cm}^2/\text{V} \cdot \text{s}$ ,  $\mu_p = 109 \text{ cm}^2/\text{V} \cdot \text{s}$ ,  $V_{tp} = 0.35 \text{ V}$ ,  $V_{tp} = -0.4 \text{ V}$ , and  $V_{DD} = 1.8 \text{ V}$ .

Solution:

$$\frac{W_p}{W_n} = \frac{360 \text{ cm}^2/V}{109 \text{ cm}^2/V} \left[ \frac{1 - \frac{2(0.35)}{1.8}}{1 - \frac{2|-0.4|}{1.8}} \right]^2 = 4.0$$

# CMOS Inverter V<sub>OH</sub> and V<sub>OL</sub>

- $\Box$  How to compute gain at  $V_{OH}$  and  $V_{OL}$  in CMOS logic gate?

- In an ideal CMOS inverter V<sub>OH</sub> is V<sub>DD</sub> and V<sub>OL</sub> is zero.

- In a resistive NMOS inverter or any non-CMOS inverter  $V_{OH}$  and  $V_{OL}$  needs to be computed.

- V<sub>OH</sub> is the output of inverter when the input is zero.

- V<sub>OL</sub> is the output of the inverter when the input is V<sub>DD</sub>.

# CMOS Inverter V<sub>IH</sub> and V<sub>IL</sub>

- $\Box$  How to compute gain at  $V_{IH}$  and  $V_{IL}$  in CMOS logic gate?

- $V_{IL}$  is the input voltage when the slope of VTC becomes -1 at the lower input voltage.

- V<sub>IH</sub> is the input voltage when the slope of VTC becomes -1 at the higher input voltage.

- Usually it is not easy to find V<sub>IH</sub> is V<sub>IL</sub> in CMOS inverter.

- However, there is an approximation technique to find  $V_{IH}$  is  $V_{IL}$  that we will discuss in the next lecture.

### **Current Transfer Characteristics**

#### CMOS Inverter Peak Current

- ☐ How to compute peak current in CMOS logic gate?

- Use current equation in saturation and use V<sub>M</sub>

- Assume long channel model, we will get:

$$I_{DD} = \frac{K'_n}{2} \left(\frac{W}{L}\right)_n (V_M - V_{Tn})^2 = \frac{K'_p}{2} \left(\frac{W}{L}\right)_p \left(V_{DD} - V_M - \left|V_{Tp}\right|\right)^2$$