# ECE321 – Electronics I

#### **Lecture 13: CMOS Inverter: Dynamic Power**

#### **Payman Zarkesh-Ha**

Office: ECE Bldg. 230B Office hours: Tuesday 2:00-3:00PM or by appointment E-mail: <u>pzarkesh.unm.edu</u>

ECE321 - Lecture 13

University of New Mexico

### **Review of Last Lecture**

- Propagation Delay

- □ Rise and Fall Times

- □ Input and Self Loading (Load) Capacitances

- **Delay Approximation**

### Today's Lecture

□ Mostly Review of Lecture 2 for Dynamic Power Calculation

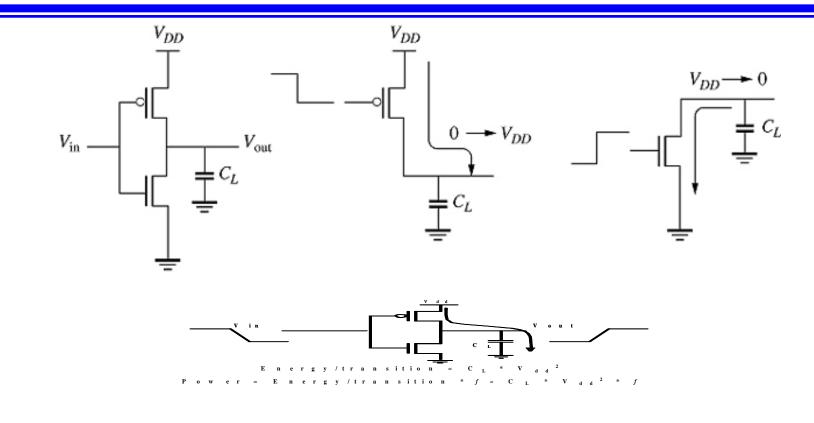

# **CMOS Dynamic Power Consumption**

$$P_{d} = \frac{1}{T} \int_{0}^{T} i_{VDD}(t) \cdot V_{DD} dt = \frac{V_{DD}}{T} \int_{0}^{T} C_{L} \frac{dV_{out}}{dt} dt = \frac{C_{L}V_{DD}}{T} \int_{0}^{V_{DD}} dV_{out} = \frac{C_{L}V_{DD}^{2}}{T} = C_{L}V_{DD}^{2} f$$

$\hfill\square$  Need to reduce  $C_L$  ,  $V_{DD},$  or f to reduce power

# **Computing Active Power**

For clock circuit that toggles twice in each period (low-to-high and high-to-low), the active power consumption is computed as:

$$\boldsymbol{P}_{active} = \boldsymbol{C}_L \boldsymbol{V}_{DD}^2 \boldsymbol{f}$$

For non-clock circuits that toggles occasionally (with probability of α) once in each period, the active power consumption is computed as:

$$\boldsymbol{P}_{active} = \frac{1}{2} \alpha \boldsymbol{C}_{L} \boldsymbol{V}_{DD}^{2} \boldsymbol{f} = \frac{1}{2} (\alpha_{0 \to 1} + \alpha_{1 \to 0}) \boldsymbol{C}_{L} \boldsymbol{V}_{DD}^{2} \boldsymbol{f}$$

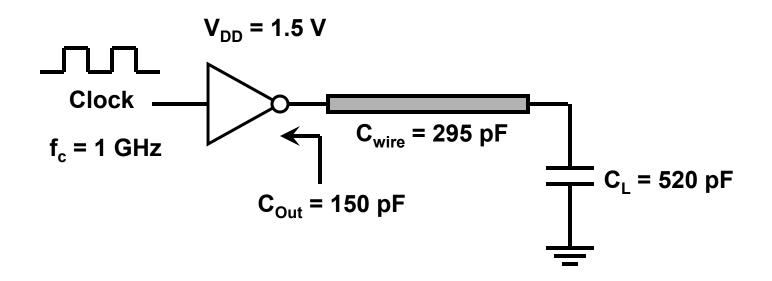

#### Example: Active Power in a Clock Driver

In this circuit, compute the power consumption in the inverter.

Answer: 2.17 W

# Minimum Power Design Techniques

- □ Prime choice: Reduce voltage!

- Recent years have seen an acceleration in supply voltage reduction

- Design at very low voltages still open question (0.6 ... 0.9 V by 2015!)

- □ Reduce switching activity

- □ Reduce physical capacitance

- Reduce clock frequency, but use multi-core architecture to enhance performance