# ECE321 - Electronics I

# Lecture 14: CMOS Inverter: Short Circuit Power

#### Payman Zarkesh-Ha

Office: ECE Bldg. 230B

Office hours: Tuesday 2:00-3:00PM or by appointment

E-mail: <u>pzarkesh.unm.edu</u>

#### Review of Last Lecture

■ Mostly Review of Lecture 2 for Dynamic Power Calculation

# Today's Lecture

- □ Short Circuit Power Analysis

- ☐ Short Circuit Power Reduction Techniques

## **CMOS Short Circuit Power Consumption**

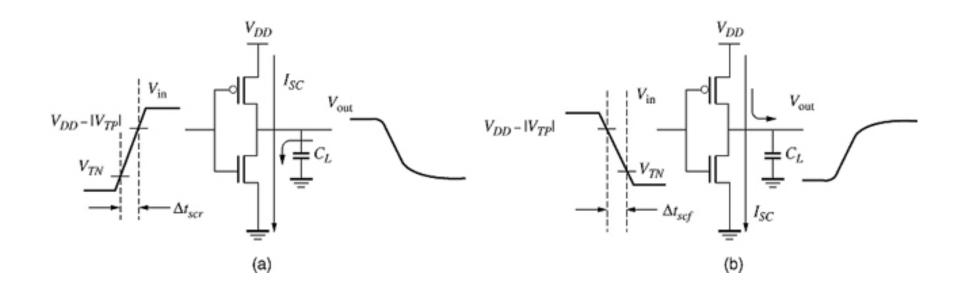

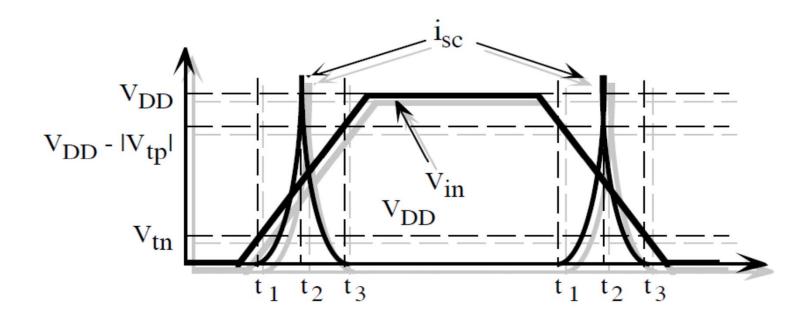

- □ Short circuit or crowbar current is the current that flows directly from VDD to GND during switching transition, when both transistors are ON, i.e. V<sub>tn</sub><V<sub>in</sub><V<sub>DD</sub>-V<sub>tp</sub>

- □ Short circuit current can be significantly large when NMOS and PMOS are large. (Why?)

#### **Computing Short-Circuit Power**

□ For clock circuit that toggles twice in each period (low-to-high and high-to-low), the active power consumption is computed as:

## **Computing Short-Circuit Power**

□ Assuming a symmetric inverter, where V<sub>tn</sub>= | V<sub>tp</sub> | and K'<sub>n</sub>(W/L)<sub>n</sub>=K'<sub>p</sub>(W/L)<sub>p</sub>, then the short circuit currents for rise and fall will be symmetric, and therefore

$$I_{mean} = \frac{1}{T} \int_{0}^{T} I(t) dt = \frac{4}{T} \int_{t_{1}}^{t_{2}} \frac{K'_{n}}{2} \frac{W}{L} (V_{in}(t) - V_{t})^{2} dt$$

$$V_{in} = \frac{V_{DD}}{\tau}t$$

$t_1 = \frac{V_t}{V_{DD}}\tau$  and  $t_2 = \frac{\tau}{2}$

$$I_{mean} = \frac{K'_n}{12} \left(\frac{W}{L}\right) \frac{1}{V_{DD}} \left(V_{DD} - 2V_t\right)^3 \frac{\tau}{T} \qquad \Longrightarrow \qquad P_{sc} = V_{DD} I_{mean}$$

## Example: Short Circuit Power in an Inverter

What is the short circuit power in an inverter if:  $V_{DD} = 2 \text{ V}$ ,  $V_{tn} = -V_{tp} = 0.5 \text{ V}$ , T = 500 ps, f = 2 GHz,  $K_n = 200 \mu \text{A/V}^2$ , W/L = 2, and the pulse rise and fall times are 100 ps.

$$I_{mean} = \left(\frac{1}{12}\right)\left(\frac{200\,\mu A}{2\,V}\right)\left(\frac{2}{1}\right)\left(2 - 1\right)^3\left(\frac{100\,ps}{500\,ps}\right) = 3.33\mu A$$

SO

$$P_{sc} = 2V \times 3.33 \,\mu A = 16.7 \,\mu W$$

# Minimum SC Power Design Techniques

- □ Prime choice: Reduce voltage!

- Recent years have seen an acceleration in supply voltage reduction

- Design at very low voltages still open question (0.6 ... 0.9 V by 2015!)

- ☐ Faster rise and fall times

- Smaller transistors (will increase delay)

- ☐ Higher V₁ (will increase delay)

- Lower frequency (will decrease performance)

$$I_{mean} = \frac{K'_n}{12} \left(\frac{W}{L}\right) \frac{1}{V_{DD}} \left(V_{DD} - 2V_t\right)^3 \frac{\tau}{T}$$