# ECE321 – Electronics I

#### Lecture 15: CMOS Inverter: Leakage Power

#### **Payman Zarkesh-Ha**

Office: ECE Bldg. 230B Office hours: Tuesday 2:00-3:00PM or by appointment E-mail: <u>pzarkesh.unm.edu</u>

ECE321 - Lecture 15

University of New Mexico

Slide: 1

### **Review of Last Lecture**

- □ Short Circuit Power Analysis

- □ Short Circuit Power Reduction Techniques

### Today's Lecture

□ Leakage Current and Power

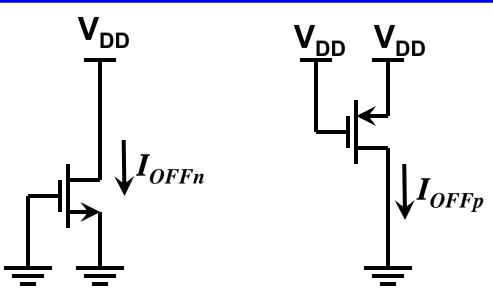

## Leakage in MOSFETs

- □ MOSFET consists of two diodes connected back to back, one in forward and the other one in reverse bias.

- ❑ When the transistors is off, V<sub>GS</sub><V<sub>T</sub>, the reverse biased diode will draw current, which is called "leakage current" or "off current".

- I<sub>OFF</sub> is heavily dependent on threshold voltage. Higher threshold voltage results in lower leakage, but lower performance too.

ECE321 - Lecture 15

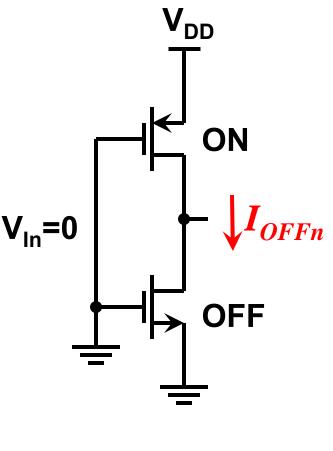

## Leakage in CMOS Inverter (V<sub>in</sub>=0)

- When the input of a CMOS inverter is at 0, PMOS is ON and can deliver any current.

- NMOS is OFF and will draw I<sub>OFFn</sub> leakage from the power supply.

- The leakage power consumption in this case is equal to I<sub>DC</sub>·V<sub>DD</sub>

$I_{DC} = I_{OFFn}$

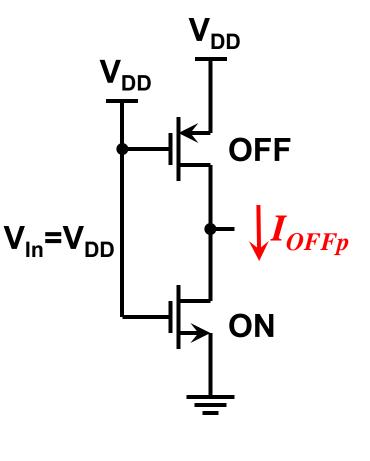

## Leakage in CMOS Inverter (V<sub>in</sub>=V<sub>DD</sub>)

- When the input of a CMOS inverter is at V<sub>DD</sub>, NMOS is ON and can deliver any current.

- PMOS is OFF and will draw I<sub>OFFp</sub> leakage from the power supply.

- The leakage power consumption in this case is equal to I<sub>DC</sub>·V<sub>DD</sub>

I<sub>DC</sub>=I<sub>OFFp</sub>

## Leakage Power in CMOS Inverter

- □ The amount of leakage power in a CMOS inverter is input dependent.

- Assuming that the probability of input being 0 and VDD is 50% each, then the average leakage power will be:

$$\mathbf{P}_{\text{leak}} = \mathbf{I}_{\text{DC,av}} \cdot \mathbf{V}_{\text{DD}} = (\mathbf{0.5}^* \mathbf{I}_{\text{OFFn}} + \mathbf{0.5}^* \mathbf{I}_{\text{OFFp}}) \cdot \mathbf{V}_{\text{DD}}$$

Sometimes, IOFF of a MOS transistor is normalized to the width of the transistor, W. In this case you need to multiply it by the width to get the actual current.

#### Example: Leakage Power in an Inverter

□ Compute the average leakage power in a CMOS inverter, where (W/L)<sub>n</sub>=10, (W/L)<sub>p</sub>=15, I<sub>OFFn</sub>=27nA/µm, and I<sub>OFFp</sub>=32nA/µm. The inverter uses 1.2V supply voltage and is implemented in 65nm technology node.

$$\mathbf{P}_{\text{leak}} = \mathbf{I}_{\text{DC,av}} \cdot \mathbf{V}_{\text{DD}} = (\mathbf{0.5*I}_{\text{OFFn}} + \mathbf{0.5*I}_{\text{OFFp}}) \cdot \mathbf{V}_{\text{DD}}$$

$\mathsf{P}_{\mathsf{leak}} = (0.5^*27 \mathrm{x} 10^{-9} \mathrm{x} (10^*65 \mathrm{x} 10^{-3}) \mathrm{+} 0.5^*32 \mathrm{x} 10^{-9} \mathrm{x} (15^*65 \mathrm{x} 10^{-3})) \mathrm{x} 1.2$

P<sub>leak</sub> = 29.25 nW

□ If we have a design with effectively 200 million inverter, how much the total leakage power will be.

## Minimum Leakage Power Design Techniques

- □ Prime choice: Threshold Voltage increase, or I<sub>OFF</sub> reduction

- This will impact the performance too (Check delay equation)

- Power supply reduction

- □ Smaller transistors (will increase delay)

- □ Higher V<sub>t</sub> (will increase delay)