# ECE321 – Electronics I

#### **Lecture 18: Interconnect Modeling II**

#### **Payman Zarkesh-Ha**

Office: ECE Bldg. 230B Office hours: Tuesday 2:00-3:00PM or by appointment E-mail: <u>pzarkesh.unm.edu</u>

ECE321 - Lecture 18

### **Review of Last Lecture**

- □ Interconnect Resistance

- □ Interconnect Capacitance

- □ Interconnect Inductance

### Today's Lecture

- Miller Effect

- □ Interconnect Delay

- **Elmore Delay**

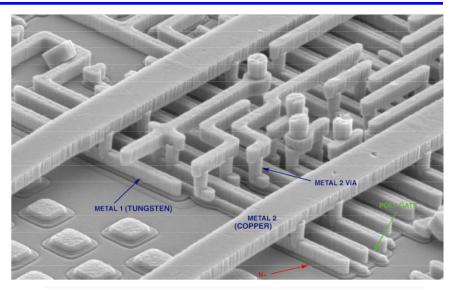

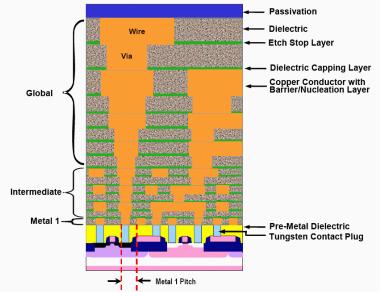

# Interconnect Complexity

- Interconnects are getting more complex as technology improves

- Current technology can have 12 layers of metal ranging from 1um to 10,000um length

- Wire pitch is 90nm for 45nm technology node

| Technology                  | 65 nm<br>(now) | 45 nm<br>(2008) | 32 nm<br>(2010) |

|-----------------------------|----------------|-----------------|-----------------|

| Wire width                  | 65 nm          | 45 nm           | 32 nm           |

| Wire<br>Thickness           | 115 nm         | 80 nm           | 60 nm           |

| Total<br>Number of<br>Wires | 60 Million     | 150 Million     | 300 Million     |

| Total wire<br>length        | 1 mile         | 1.4 mile        | 2 mile          |

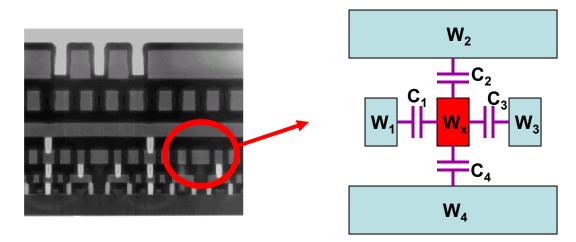

#### **Effective Capacitance & Miller Effect**

□ If  $W_1$ ,  $W_2$ ,  $W_3$ , and  $W_4$  are grounded (not switching), then the total capacitance that the  $W_x$  wire sees is:

$$C_x = C_1 + C_2 + C_3 + C_4$$

□ If  $W_2$ , and  $W_4$  are grounded but  $W_1$  and  $W_3$  switches in the <u>same direction</u> of  $W_x$ , then the total capacitance that the  $W_x$  wire sees is:

$$C_x = C_2 + C_4$$

□ If  $W_2$ , and  $W_4$  are grounded but  $W_1$  and  $W_3$  switches in the <u>opposite direction</u> of  $W_x$ , then the total capacitance that the  $W_x$  wire sees is:

$$C_x = 2C_1 + C_2 + 2C_3 + C_4$$

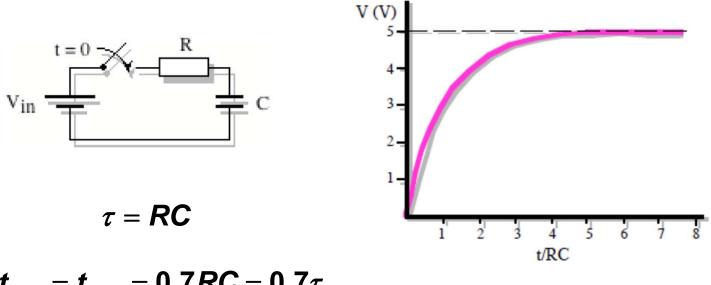

#### Interconnect Time Constant & Delay

- □ Interconnect circuit can be simplified as an RC network.

- **D** The time constant of an interconnect is simply  $\tau = RC$

- However, the propagation delay of an RC interconnect is 0.7RC. Why?

$t_{_{PHL}} = t_{_{PLH}} = 0.7 RC = 0.7 \tau$

\* Beware that in Prof. Hawkins book the time constant is sometimes called propagation delay

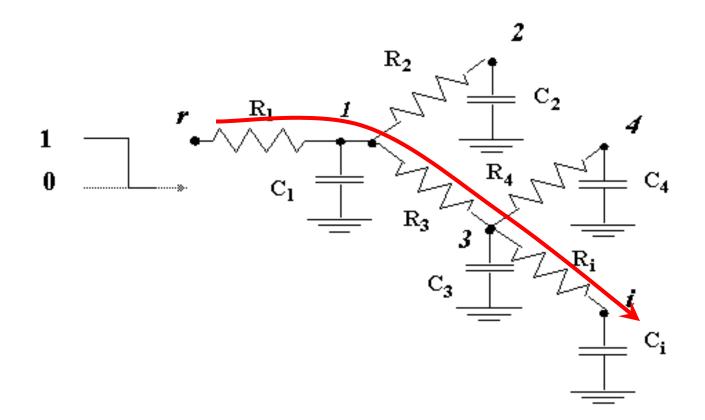

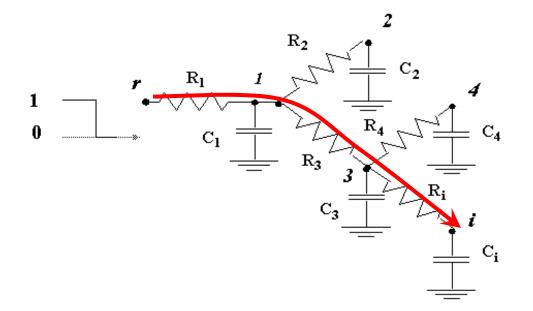

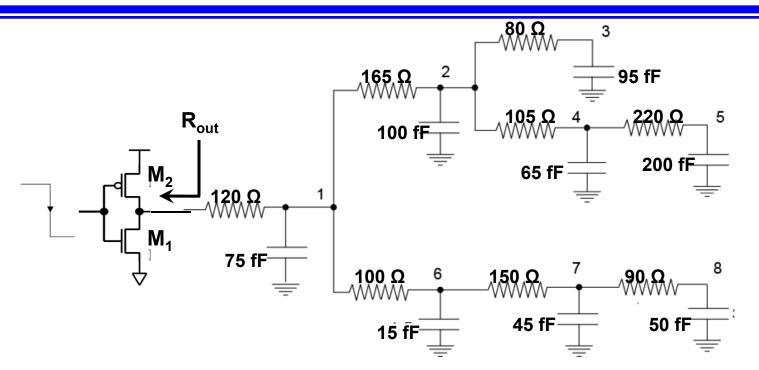

### **Real Interconnect Circuit Model**

How to compute the delay from node r to node I in this complex RC network?

Answer: Use Elmore delay formula!

ECE321 - Lecture 18

### **Elmore Delay Formula**

$$R_{ik} = \sum R_j \Longrightarrow (R_j \in [path(s \to i) \cap path(s \to k)])$$

$$\tau_{Di} = \sum_{k=1}^{N} C_k R_{ik}$$

$$\tau_{Di} = R_1 C_1 + R_1 C_2 + (R_1 + R_3) C_3 + (R_1 + R_3) C_4 + (R_1 + R_3 + R_i) C_i$$

ECE321 - Lecture 18

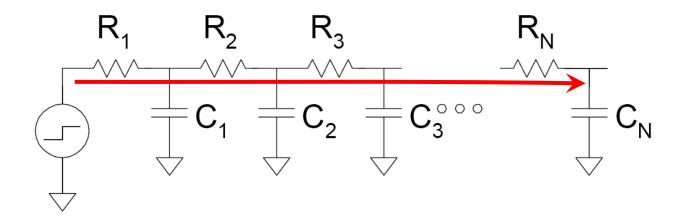

#### Example 1: Elmore Delay in RC Ladder

$$\tau_{Di} = \sum_{k=1}^{N} R_{ki} C_k$$

=  $R_1 C_1 + (R_1 + R_2) C_2 + \dots + (R_1 + R_2 + \dots + R_N) C_N$

ECE321 - Lecture 18

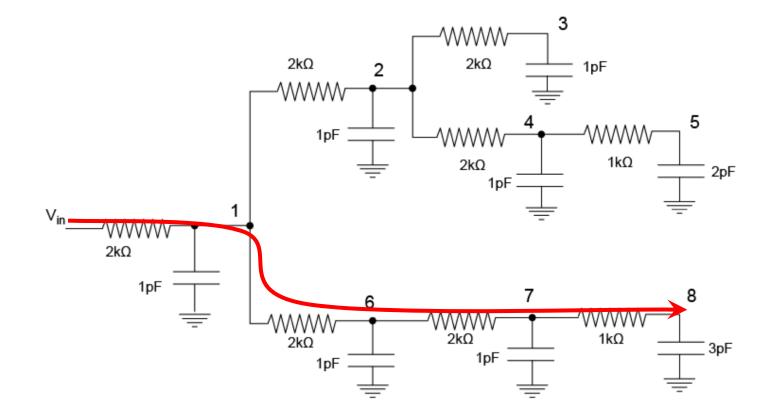

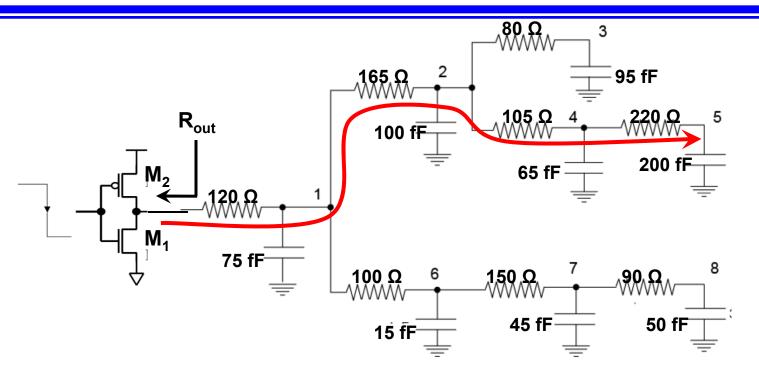

### Example 2: Another Elmore Delay

Try this example by yourself. The time constant from Vin to node 8 is 43ns. Therefore, the propagation delay from Vin to node 8 is 30.1 ns

# **Open Question:**

- When an inverter is driving an interconnect, it is better to model the gate as a resistor.

- □ Based on what you have learned so far, how do you compute the effective output resistance of an inverter?

- Rout is one of the parameters in inverter cell characterization in Electronic Design Automation (EDA) tools.

# Homework 15

- □ Assume that  $V_{DD}$ =1.5 V, K'<sub>n</sub>=100 uA/V<sup>2</sup>, Vt<sub>n</sub>=0.4 V,  $\lambda_n$ =0.1 V<sup>-1</sup>, (W/L)<sub>n</sub>=10, K'<sub>p</sub>=60 uA/V<sup>2</sup>, Vt<sub>p</sub>=-0.4 V,  $\lambda_p$ =0.2 V<sup>-1</sup>, (W/L)<sub>p</sub>=17. Find R<sub>out</sub>. Hint: connect a load of 100fF to the gate, calculate the LH propagation delay (t<sub>pLH</sub>) using average current technique, then equate the propagation delay to a simple RC network and find R<sub>out</sub>. This will effectively be R<sub>out</sub>(LH).

- □ Use Elmore technique to compute the time constant and LH propagation delay (t<sub>PLH</sub>) of the above network from the gate input to node 5.