# ECE321 – Electronics I

#### **Lecture 4: Physics of Semiconductor Diodes**

#### **Payman Zarkesh-Ha**

Office: ECE Bldg. 230B Office hours: Tuesday 2:00-3:00PM or by appointment E-mail: <u>pzarkesh.unm.edu</u>

ECE321 - Lecture 4

University of New Mexico

#### **Review of Last Lecture**

- **Electrical Property of Materials**

- **Energy Band Diagrams**

- □ Semiconductor Materials

- □ n-Type and p-Type Semiconductor Materials

- □ Mass Action Law

# Today's Lecture

- **Carrier Transport in Semiconductors**

- **Drift Current**

- **Diffusion Current**

- **PN** Junction

- **Depletion Region**

- □ Reverse Biased PN Junction

- Forward Biased PN Junction

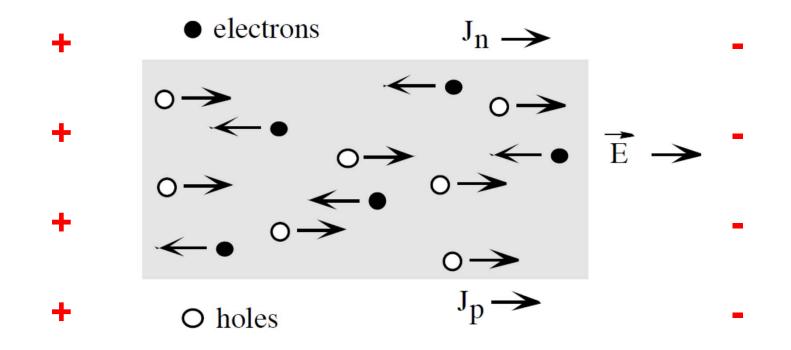

# **Drift Current Due to Electric Field**

- □ This is what happens in a typical resistors

- Direction of electrons and holes under externally applied electric field (E) is shown below

#### **Drift Current Equations in Semiconductor**

*n*-type silicon has  $n_o \approx N_D = 10^{17}$  (atoms/cm<sup>3</sup>) at 300 K,  $\mu_n = 1350$  cm<sup>2</sup>/V•s,  $\mu_p = 480$  cm<sup>2</sup>/V•s, and the electric field is 10 V/cm. (a) What is the minority hole carrier density  $p_o$  (b) What is the total current density J? (c) What is the resistivity of the material?

Solution

(a)

$$p_o = \frac{n_i^2}{n_o} = \frac{(1.062 \times 10^{10})^2}{10^{17}} = 1.128 \times 10^3 \left(\frac{\text{holes}}{\text{cm}^3}\right)$$

(c)  $J = \sigma E = \frac{1}{\rho} E$

$216 = 10 / \rho \rightarrow \rho = 46.3 \text{ m}\Omega \cdot \text{cm}$

*Ref:*

$$\rho_{cu} = 1.7 \ \mu\Omega \cdot cm$$

1

$$J = (1350)(1.6 \times 10^{-19})(10)(10^{17}) + (480)(1.6 \times 10^{-19})(10)(1.128 \times 10^{3})$$

$$= 216 + 8.7 \times 10^{-13} = 216 \left(\frac{A}{cm^2}\right)$$

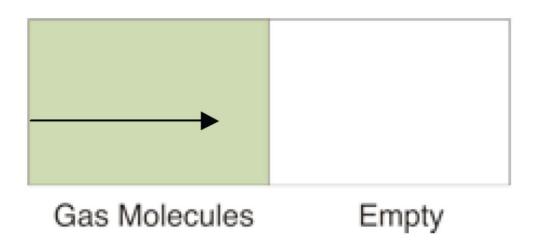

### **Diffusion Current Due to Density Gradient**

- This happens when the carrier concentration is different from one side to the other side

- □ An analogous case happens in gas container below, where the gas molecules "diffuses" from higher density to lower density

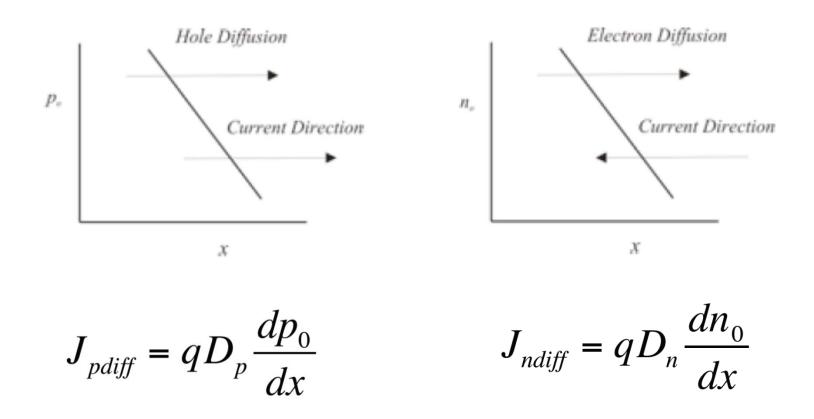

### **Diffusion Current Equations**

$D_n$  and  $D_p$  are the electron and hole "diffusion constants"

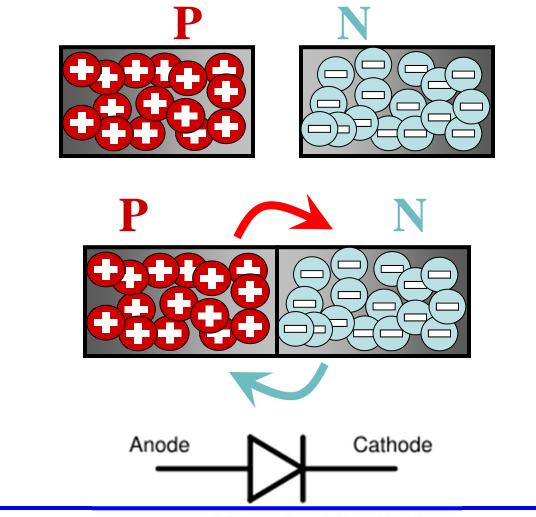

### **PN Junction**

What does happen when P-Type semiconductor meets N-Type Semiconductor?

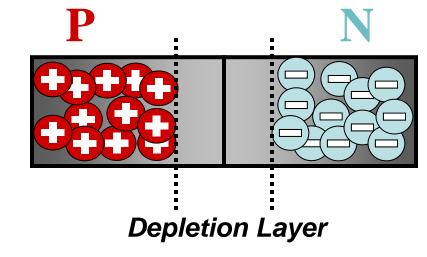

# **PN Junction**

- Some electrons will cross the junction and fill holes. A pair of ions is created each time this happens.

- □ As this ion charge builds up, it prevents further charge migration across the junction.

- □ The junction goes into equilibrium when the barrier potential prevents further diffusion.

- ❑ At 25 degrees C, the barrier potential for a silicon pn junction is about 0.5 to 0.7 volts.

### **Depletion Region in Equilibrium**

□ The barrier potential across deletion region is computed as:

$$V_{bi} = V_{th} Ln \left( \frac{N_A \cdot N_D}{n_i^2} \right) \qquad V_{th} = \frac{kT}{q}$$

□ The width of depletion region is computed as:

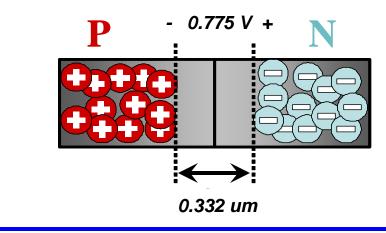

#### **Example: Depletion Region**

□ Calculate the built-in potential and depletion width at 300K in a diode if  $n_i$ =1.062x10<sup>10</sup> cm<sup>-3</sup>,  $\epsilon_{si}$  = 1.04x10<sup>-12</sup> F/cm ,  $N_A$ =10<sup>16</sup> cm<sup>-3</sup>, and  $N_D$  = 10<sup>17</sup> cm<sup>-3</sup>.

$$V_{bi} = V_{th} Ln \left( \frac{N_A \cdot N_D}{n_i^2} \right) = 0.026 Ln \left( \frac{10^{16} \cdot 10^{17}}{\left( 1.062 \times 10^{10} \right)^2} \right) = 0.775 V$$

$$W = \sqrt{\frac{2\varepsilon_{si}}{q} \frac{N_A + N_D}{N_A \cdot N_D}} V_{bi} = \sqrt{\frac{2 \times 1.04 \times 10^{-12}}{1.609 \times 10^{-19}} \frac{10^{16} + 10^{17}}{10^{16} \cdot 10^{17}} \times 0.775} = 3.32 \times 10^{-5} cm = 0.332 um$$

### **Depletion Region Phenomena**

- The depletion region is so named because it is formed by removal of all free charge carriers leaving none to carry a current.

- Depletion region is therefore an insulator region within a conductive material.

- Many modern semiconductor devices function based on "depletion region" phenomena.

- Example: Diodes, Solar cells, Bipolar Transistors, and MOS Transistors, Variable Capacitance Diodes

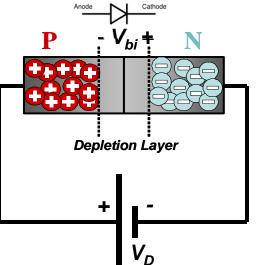

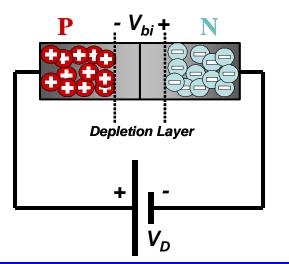

# **PN Junction Under Applied Voltage**

- □ The applied external voltage, V<sub>D</sub>, on the diode will directly affects the built-in potential

- In reverse bias, the external voltage adds up to the built-in potential increasing the effect of V<sub>bi</sub>

- In forward bias, the external voltage is against the built-in potential reducing the effect of V<sub>bi</sub>

- Depletion region width also depends on the voltage applied to the diode.

- **Review**:

$$W = \sqrt{\frac{2\varepsilon_{si}}{q} \frac{N_A + N_D}{N_A \cdot N_D} (V_{bi} - V_D)}$$

$$V_{bi} = V_{th} Ln \left(\frac{N_A \cdot N_D}{n_i^2}\right) \qquad V_{th} = \frac{kT_A}{q}$$

ECE321 - Lecture 4

University of New Mexico

#### **Reverse Biased PN Junction**

- □ In CMOS transistors, that are currently used in semiconductor industry, all PN junctions are normally in reverse bias condition.

- □ When V<sub>D</sub><0 the width of depletion region increases which results in no conduction.</p>

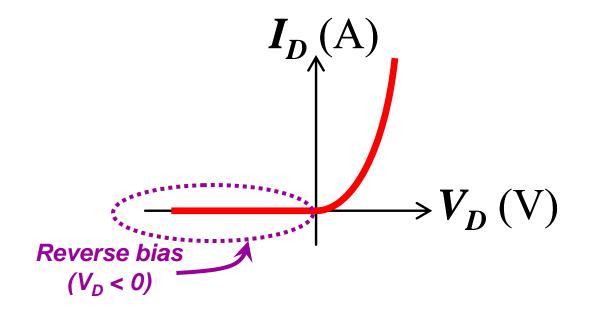

#### Forward Biased PN Junction

- **When**  $0 < V_D < V_{bi}$  the width of depletion region decreases.

- □ Once V<sub>D</sub>>=V<sub>bi</sub>, then depletion region disappears and the diode starts conducting.

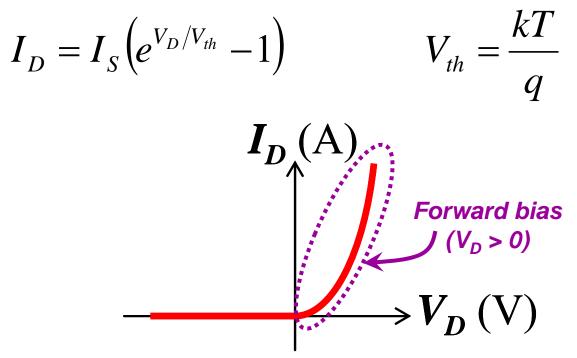

- The current in a diode can then be approximated as:

#### **Diode's Parasitic Capacitance**

- □ The depletion region, which act as an insulator, behaves like a capacitor in a PN junction.

- □ The "junction capacitance" can be calculated as:

$$C_{j} = \frac{\varepsilon_{si}A}{W} = \frac{\varepsilon_{si}A}{\sqrt{\frac{2\varepsilon_{si}}{q}\frac{N_{A}+N_{D}}{N_{A}\cdot N_{D}}}} \left(V_{bi}-V_{D}\right) = \frac{A\sqrt{\frac{q\varepsilon_{si}}{2}\frac{N_{A}\cdot N_{D}}{N_{A}+N_{D}}}}{\sqrt{1-\frac{V_{D}}{V_{bi}}}} = \frac{C_{j0}}{\sqrt{1-\frac{V_{D}}{V_{bi}}}}$$

Where:

$$V_{bi} = V_{th} Ln \left( \frac{N_A \cdot N_D}{n_i^2} \right) \qquad \qquad V_{th} = \frac{kT}{q}$$

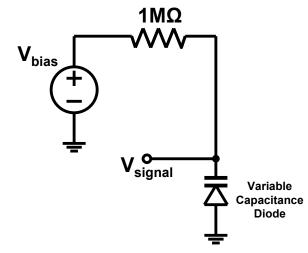

### Variable Capacitance Diode (Varactor)

- □ Generally, the junction capacitance in a diode is undesirable because it slows down the switching of the diode.

- □ Sometimes, we make a good use of this "parasitic capacitance".

- The capacitance of a reverse bias diode can be adjusted by the amount of bias on a diode.

- If the AC input signal is small enough, the reverse bias diode can be seen as a capacitor, whose value can be adjusted by its reverse bias voltage.

#### **Small Signal Model for Diodes**

$$I_D = I_S \left( e^{V_D / V_{th}} - 1 \right) \qquad \qquad V_{th} = \frac{kT}{q}$$

#### **Dynamic (Small Signal) Conductance**

$$g_{d} = \left(\frac{dI_{D}}{dV_{D}}\right)_{V_{D} = V_{Q}} = \frac{I_{S}}{V_{th}}e^{V_{Q}/V_{th}} \approx \frac{I_{Q}}{V_{th}}$$

Dynamic (Small Signal) Resistance

$$r_d = \frac{1}{g_d} = \frac{V_{th}}{I_Q}$$

I<sub>D</sub>

$I_0$

$V_{0}$

$V_{D}$

University of New Mexico

Slide: 18